SIMULATION SERVICES

Signal Integrity AnalysisSignal Integrity enables engineers to quickly and accurately analyze and eliminate signal integrity and EMI/EMC design problems early in the design cycle. Our Signal Integrity comes ready to use in virtually any PCB design flow and offers unprecedented time-to-results, improving productivity, reducing development and product costs, and increasing product performance. SI analysis to meet the design specifications in respect of timing, skew, crosstalk and signal distortions. ELDAAS combines SI tools and design expertise, coupled with constraint managed design paradigm, to address complex engineering tasks. This ensures “First Time Right Designs” and reduces time to market. The interconnects operating at high frequency and fast switching rates demand SI analysis for right design at first time. ELDAAS’s SI engineers are having strong knowledge in SI theory and expertise in simulation tools to analyse various SI issues like reflection due to impedance mismatch, crosstalk, signal attenuation and PDN noise which affects the interconnect performance. The SI analysis is carried out in two phase, the pre and post layout analysis. Pre-layout Analysis: Planning the stack-up for controlled impedance, dielectric material selection for high frequency operation, I/O buffer selection from different derive strength, topology optimization, termination strategy, routing specifications (Trace width, spacing and length matching) and floor planning for critical components are various sections in pre-layout analysis. Post layout Analysis: Simulation of routed board for potential SI issues like reflection, overshoot/undershoot, crosstalk, attenuation and EMI issues. The post layout report is prepared from simulation results along with suggestions for topology modification, termination schemes and layout modification to achieve good signal integrity for any SI issues. For Printed Circuit BoardsSignal Integrity Analysis

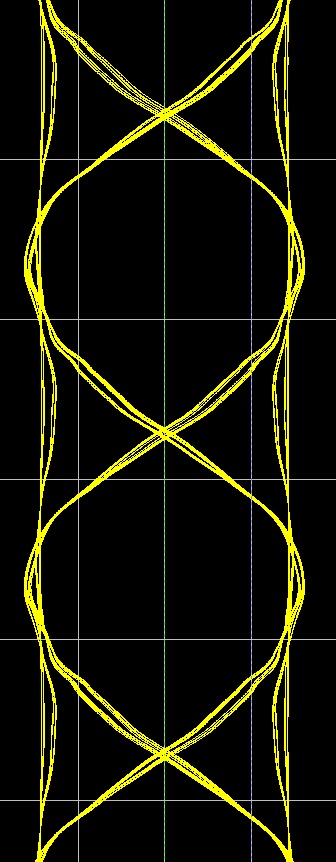

Single ended and Differential Crosstalk Analysis Signal Attenuation due to IR-Drop, Skin-effect and Dielectric Loss Channel Analysis for Serial Communication – Eye Diagram Analysis

Timing Analysis

Common clocking (PCI, FSB) Source synchronous clocking (DDR)

Power Integrity Analysis

IR- Drop Analysis Power Distribution Network Impedance profile Analysis De-coupling Capacitors Estimation and Placement Optimization Various Interfacing TechnologiesParallel Technologies

PCI, PCI-X SDRAM, QDR, DDR, DDR2 3 FSB, Hub Interface

Serial Technologies

USB, PCIe, HT, SATA SERDES, XAUI, RocketIO, Aurora, Gigabit Ethernet SRIO, CPRIO

Signal and Power Integrity Analysis

Reflection and Ringing Analysis Single and Differential Crosstalk Analysis De-coupling Capacitors Estimation and Placement Optimization

|

|---|